#### 【書類名】 明細書

【発明の名称】有限窓 Fejer-Yukawa カーネルによる UWP (Uniform Window Positivity) 制約下の適応信号処理方法、信号処理装置、及びプログラム

#### 【技術分野】

## [0001]

本発明は、デジタル信号処理(DSP)及び時系列データの前処理・評価に関し、特に、全タップ非負かつ L1 正規化された有限窓カーネル(Fejer-Yukawa カーネル)を用いて、UWP(Uniform Window Positivity)制約(例:RMS と negative portion ratio による基準)を満たすように適応的にパラメータを更新しつつ、FFT 等による畳み込み、決定実行(deterministic execution)及び監査ログ出力を行う信号処理方法、これを実装する信号処理装置、並びに当該方法を実行させるプログラム及び記録媒体に関する。さらに、本発明は、CIC/IIR によるハードウェア近似、FPGA/ASIC/SoC における固定小数点実装、polyphase パイプライン、並びに RC/スイッチトキャパシタ等を用いた混載(アナログ+デジタル)構成にも関する。適用分野として、電力系統・EV フリート等のエネルギー分野、通信・レーダ/ソナー、医用(ECG/EEG)、画像・センシング、ロボティクス制御、金融時系列解析等、広範な産業領域を包含する。

## 【背景技術】

## [0002]

従来、電力系統監視、車載・ロボティクス制御、通信・レーダ/ソナー受信、医用信号 (ECG/EEG)、画像・センシング、金融ティックなど、多様な時系列に対して、移動平均や各種窓関数 (Hann, Hamming, Blackman 等)、FIR/IIR フィルタ、指数平滑、Savitzky-Golay、カルマン系フィルタが用いられてきた。これらはノイズ低減、帯域制御、外れ値抑制、推定の安定化を目的とするものである。

#### [0003]

しかし、従来手法は「所望の平滑(コスト削減)」と「推定の一貫性(再現性・安定性)」の両立が難しい。すなわち、(i) 周波数特性における通過帯リップル・阻止帯減衰・群遅延のトレードオフ、(ii) 時間領域での負のリンギングやオーバー/アンダーシュート、(iii) ハイパーパラメータ選択に経験則が多く、データ条件が変わると挙動が不安定、等の課題がある。

## [0004]

さらに、実運用では並列計算・FFT 計画・乱数シード・スレッド配置等が結果の非決定性を生み、実行の再現性が確保されにくい。ログ出力や設定固定の仕組みは存在するものの、信号前処理アルゴリズムに統合され、品質指標と連動して「再現性を装置特性として担保する」枠組みは一般的ではない。

#### [0005]

計算資源の観点でも、長い FIR や高次数 IIR、あるいは大規模 FFT 畳み込みは、エッジ /組込み環境や省電力デバイスで負担が大きい。固定小数点実装では、係数の符号反転や加 算キャンセルに起因するビット幅膨張・オーバフロー解析・サチュレーション設計が煩雑 になりやすい。ハードウェア(IP コア/FPGA/ASIC)では乗算器数の抑制、レイテンシの上限 保証、スループットの一定化が要請される。

## [0006]

正値性(タップ全非負)の観点では、移動平均(CIC)のような非負カーネルは存在するが、阻止帯抑圧が弱い、あるいは単独では望ましい時定数設計が難しいという課題がある。一方、指数平滑(IIR)は片側・因果の実装に偏り、両側(零位相近似)の整形と統一的な規格化(例えば L1 正規化による DC ゲイン管理)が系統的に扱われないことが多い。これらを組み合わせる設計自体は知られていても、(a) 有限窓かつ全タップ非負で、(b) 規格化基準を満たし、(c) 品質指標に対する一様な正性制約(後述の UWP)を満たすよう、(d) コスト最小化の観点で適応的にパラメータ選定する、という一体の枠組みは十分に確立していない。

## [0007]

品質指標についても、RMS(零平均後の二乗平均平方根)や負値率(観測区間における負値サンプル比)といった、運用現場で理解しやすく設定しやすい単純指標を窓・カーネル設計と直結させ、その充足を監視・フィードバックしてパラメータ(Gamma, lambda, カーネル長M 等)を調整する制御ループは、一般的な DSP 前処理パイプラインには統合されていない。

## [0008]

ハードウェア観点では、三角窓 (Fejer) は移動平均の自己畳み込み (CIC´2) で実装可能、指数核 (Yukawa,  $\exp(-lambda|n|)$ ) は低次数 IIR の双方向等価で近似可能であるが、これらを直列カスケードして全タップ非負の有限窓を得、さらに L1 正規化で DC ゲインを一意に管理しつつ、polyphase パイプラインにより一定レイテンシ/スループットを保証し、乗算器を抑えた CSD 表現や固定小数点設計まで含めて IP コアとして体系化する試みは限定的である。

#### [0009]

混載(アナログ+デジタル)の面でも、アナログ前段で RC ネットワークにより Yukawa 近似を行い、スイッチトキャパシタ積分で Fejer 近似を行って粗整形→低ビット ADC→デジタル整形で仕上げる省電力チェーンは有用だが、これと品質指標のモニタリング、適応チューニング、決定実行(順序/並列/シード/FFT 計画等の固定)および監査ログ出力を同一の設計思想で貫くアーキテクチャは未だ一般化していない。

#### [0010]

以上のように、(1) 有限窓かつ全タップ非負・L1 正規化というハードウェア/固定小数点に親和的な核を用い、(2) 窓の一様な正性(UWP: uniform window positivity)という分かりやすい品質制約で挙動を安定化し、(3) その制約を満たす範囲で計算資源(実行時間、FLOPs等)を最小化する適応パラメータ選定を行い、(4) 並列・FFT・乱数等を固定して実行の再現性(決定実行)と監査可能性を担保し、(5) 必要に応じて混載構成まで包含する、産業横断で再利用可能な統合的信号前処理プラットフォームが望まれている。

#### 【先行技術文献】

### 【特許文献】

## [0011]

[特許文献 1] US 6,173,302 B1「Decimation method and decimation filter」- CIC

(Cascaded Integrator-Comb)によるデシメーションの高効率実装を開示。乗算器不要の構造だが、タップ全非負・L1 正規化・UWP の一体設計や決定実行/監査ログ連携は示唆されていない。

#### [0012]

[特許文献 2] US 5,596,609 「Parallel cascaded integrator-comb filter」 - CIC の並列化/ビットスライス化で高速化を図る発明。並列構成に関するが、UWP 指標を用いた適応チューニングや品質一様正性の保証は扱わない。

#### [0013]

[特許文献 3] US 4,550,295「Switched-capacitor integrator」- SC 積分器の基本構成。アナログ前段の省電力実装に有用だが、FY (二段 CIC+Yukawa) による全タップ非負の有限窓や UWP 制御ループとの統合は開示されない。

## [0014]

[特許文献 4] EP 3 579 412 A1「CIC decimation filter の改良」- CIC 系の改良例。CIC の内部制御やリセット制御を述べるが、L1 正規化・UWP・決定実行・監査ログの組合せは記載がない。

## [0015]

[特許文献 5] US 2017/0005670 A1「Low power analog-to-digital converter」- 低消費電力 ADC の構成。前段のアナログ整形と後段のデジタル FY/UWP の協調 (混載一体最適化) は触れられていない。

## 【非特許文献】

## [0016]

[非特許文献 1] F. J. Harris, "On the Use of Windows for Harmonic Analysis with the DFT," Proc. IEEE, 66(1), 1978 - 各種窓の性能比較。窓選択の基礎だが、Fejer-Yukawa の有限窓+UWPという品質制約による適応制御は対象外。

#### [0017]

[非特許文献 2] E. B. Hogenauer, "An Economical Class of Digital Filters for Decimation and Interpolation," IEEE TASSP, 29(2), 1981 - 乗算器不要の CIC を提示。UWP 指標や L1 正規化・全タップ非負の有限窓統合設計は論じない。

## [0018]

[非特許文献 3] R. E. Crochiere, L. R. Rabiner, Multirate Digital Signal Processing, Prentice-Hall, 1983 - マルチレート/ポリフェーズの古典。パイプライン化の枠組みは与えるが、決定実行(乱数・スレッド・FFT 計画の固定) + 監査ログを品質制約と結合する設計思想はない。

#### [0019]

[非特許文献 4] A. Savitzky, M. J. E. Golay, "Smoothing and Differentiation of Data by Simplified Least Squares Procedures," Analytical Chemistry, 1964 - 多項式平滑(SG)による雑音低減。滑らかさの制御は可能だが、一様正性(UWP)を用いる再現性指標や L1 正規化・全タップ非負との連携は想定しない。

## [0020]

[非特許文献 5] R. Gregorian, G. C. Temes, Analog MOS Integrated Circuits for Signal Processing, Wiley, 1986 - SC フィルタ/積分器の体系。アナログ前段の有力基盤だが、本発明が主張するアナログ (RC/SC) →低ビット ADC→デジタル FY→UWP/適応チューナの混載一体制御は扱わない。

## [0021]

以上の特許・文献はいずれも、(i) 全タップ非負かつ L1 正規化された有限窓 (Fejer-Yukawa)、(ii) UWP (Uniform Window Positivity) を品質制約として常時監視・維持、(iii) その制約内で計算資源を最小化する適応チューニング、(iv) 決定実行(乱数・FFT計画・スレッド配置の固定)と監査ログの統合、(v) ポリフェーズ固定小数点/混載(RC・SC+低ビット ADC) まで含めた一体設計という本発明の要部を開示しない。従って、本発明は品質一様正性に基づく再現性保証とコスト最小化を同時達成する統合的アーキテクチャとして、新規性・進歩性を基礎づける。

## 【発明の概要】

- 【0022】本発明は、全タップ非負かつ L1 正規化された有限窓カーネル(Fejer-Yukawa:以下「FY」)を用いて、時系列データの前処理・評価を行う統合技術に関する。FY は、移動平均の自己畳み込み( $CIC^2$ )による Fejer 成分と、指数核  $exp(-\lambda|n|)$  の双方向等価 IIR による Yukawa 成分を直列化し、DC ゲインを L1 正規化で規定することで、リンギング抑制と実装容易性(固定小数点適合)を両立する。

- 【0023】入力系列は FY 畳み込み (FFT 又はポリフェーズ・ストリーミング) を経て評価器 (DFT/コサイン和等) に供されるとともに、零平均化 RMS と負値率等から成る品質指標を用いる UWP (Uniform Window Positivity) モニタにより常時監視される。UWP が満たされない場合には、適応チューナが  $\{\Gamma, \lambda, M\}$  を制約付き最適化により更新し、品質を維持したまま実行時間・演算量・メモリアクセス等のコストを最小化する。

- 【0024】実行系は決定実行(deterministic execution)を採用し、処理順序・並列度・メモリアクセス順位・FFT 計画 ID・擬似乱数シード等を固定するスケジューラと、設定・パラメータ・実行順序のハッシュ及び時刻情報を含む監査ログ出力により、同一条件下での完全再現を装置特性として保証する。

- 【0025】ハードウェア実装では、ポリフェーズ・パイプラインにより一定レイテンシ Lと所要スループット(少なくとも f\_clk/K)を保証し、係数は CSD (canonical signeddigit)等で表現して乗算器を抑制、固定小数点ビット幅とサチュレーションを安全側に設 計する。さらに、RC ネットワーク及びスイッチトキャパシタ積分器によるアナログ近似と 低ビット ADC を前段に配した混載構成にも適用可能である。

- 【0026】以上により、本発明は、品質一様正性(UWP)に基づく安定化と、計算資源・電力・装置規模の削減、ならびに結果の再現性・監査可能性を同時に実現する。電力・エネルギー、通信、医用、画像・センシング、ロボティクス、金融等の産業分野において、ソフトウェア/ハードウェアを問わず適用できる汎用の信号処理プラットフォームを提供する。

## 【発明が解決しようとする課題】

## [0027]

第一の課題は、計算コスト(時間・FLOPs・メモリアクセス・電力)と、推定品質の一貫性 (統計的ばらつき・再現性)の同時達成が困難である点である。従来は品質を上げるとコ ストが急増し、コストを下げると品質が不安定化するトレードオフから抜け出しにくい。

## [0028]

第二の課題は、運用条件(雑音帯域・外乱・サンプル密度・窓長等)が変化した際に、出力の安定性が保証されない点である。時間領域での負リンギングや過度のオーバー/アンダーシュート、周波数領域でのリップル・群遅延のばらつきが、用途横断の標準化を阻害している。

#### [0029]

第三の課題は、並列度・スレッド割付・FFT 計画・擬似乱数シード等に依存する実行の非決定性により、同一条件下での完全再現が担保されにくい点である。これに伴い、監査可能性(実行証跡)の欠如が品質保証・規制対応・研究再現性の障害となる。

### [0030]

第四の課題は、ハードウェア実装容易性の不足である。固定小数点実装におけるビット幅膨張・飽和設計、乗算器資源の過多、一定レイテンシ/所要スループットの保証といった制約を満たしながら、所望の周波数特性を安定に確保する設計指針が不足している。

#### [0031]

第五の課題は、カーネル/窓設計やハイパーパラメータ選定が属人的で、データ条件の変化に対して自動的な再最適化が行われにくい点である。その結果、現場ごとに性能がばらつき、スケール展開を阻害する。

## [0032]

第六の課題は、アナログ前段(RC・スイッチトキャパシタ)や低ビット ADC との一体最適 化の不足である。前段での粗整形と後段デジタル処理の分断により、電力・データ量・装 置規模の最小化が十分に進まない。

## [0033]

第七の課題は、設計仕様(例:ω\_p、ω\_s、リップル Rp、減衰 As)と運用指標(例:零平均化 RMS、負値率)の橋渡しが体系化されていないため、品質保証や受入試験での判定基準を合意しにくい点である。

#### [0034]

第八の課題は、ソフトウェア(CPU/GPU)・ハードウェア(FPGA/ASIC/SoC)・混載(アナログ+デジタル)・記録媒体(プログラム製品)という実装形態の違いを跨いで一貫に適用できる枠組みが欠如しており、産業横断の再利用性が低い点である。

### 【課題を解決するための手段】

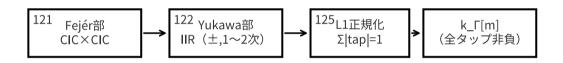

【0035】本発明は、全タップ非負かつ L1 正規化 (sum of taps = 1) の有限窓カーネルである Fejer-Yukawa (以下 FY) を核とし、Uniform Window Positivity (UWP) 制約を品質ハブに据えた方法・装置・プログラムの一体構成を提供する。FY は Fejer 部 (CIC<sup>2</sup>に相当)と Yukawa 部 (exp(-lambda\*|n|) を両側 IIR(1-2 次)で近似)を直列カスケー

ドし、L1 正規化で DC ゲインを規定する([図 2])。

#### [0036]

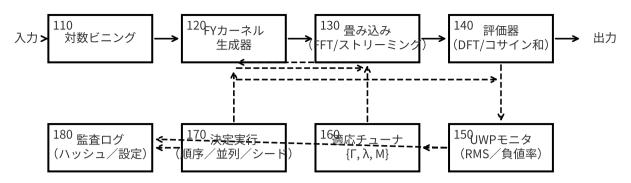

(方法の構成)本発明の方法は、入力系列 x を対象に、以下の工程 S1からS7 を含む ([図 1])。

S1:FY カーネル生成 (パラメータ set {Gamma, lambda, M}、全タップ非負、L1 正規化)。

S2: FY 畳み込み (FFT 又はストリーミング/ポリフェーズ) により前処理を実行。

S3:評価器により所定の統計量を算出(例:DFT/コサイン和、相関等)。

S4: UWP モニタにて、零平均化 RMS と negative portion ratio (負値率) 等の閾値判定を行い、適合/不適合フラグを生成。

S5:不適合の場合、適応チューナが {Gamma, lambda, M} を制約付き最適化で更新(目的: 実行コスト最小化、制約: UWP 満足)。

S6:決定実行 (deterministic execution) により、処理順序・並列度・メモリアクセス順位・FFT 計画 ID・PRNG シード等を固定し、同一条件で同一出力を保証。

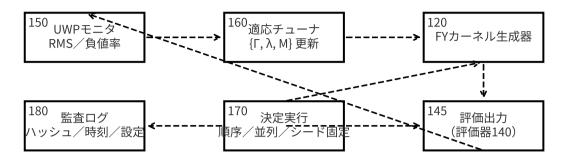

S7:監査ログに設定・パラメータ・実行順序のハッシュと時刻情報を逐次記録し、再現・ 検証・規制対応を支援([図3])。

## [0037]

(装置の構成)本発明の信号処理装置は、上記 S1から S7 に対応するモジュールを備える。すなわち、FY カーネル生成部、畳み込みエンジン(FFT/ストリーミング)、評価器、UWP モニタ、適応チューナ、決定実行スケジューラ、監査ログ出力部から構成される([図1][図3])。装置は CPU/GPU/FPGA/ASIC/SoC のいずれにも実装可能である。

#### [0038]

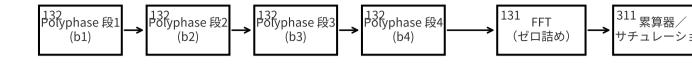

(固定小数点・レイテンシ保証)ストリーミング経路はポリフェーズ・パイプラインで構成し、所定の一定レイテンシ L と必要スループット( $\gt= f_c lk/K$ )を設計上保証する。係数は CSD 等で表現し乗算器を抑制、ビット幅スケジュールとサチュレーションは安全側に設定する([図 5])。

#### [0039]

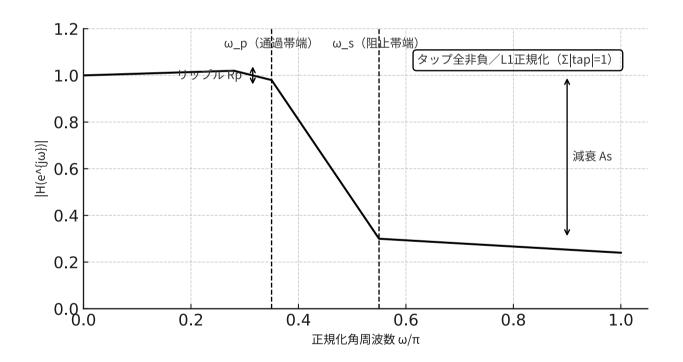

(周波数仕様の保持) FY カーネルの {Gamma, lambda, M} は、通過帯端 omega\_p、阻止帯端 omega\_s、通過帯リップル Rp、阻止帯減衰 As の仕様域を満たすよう選定できる([図4])。この仕様は UWP 制約 (RMS、負値率等) と連動し、適応チューナが仕様逸脱時に自動補正を行う。

#### [0040]

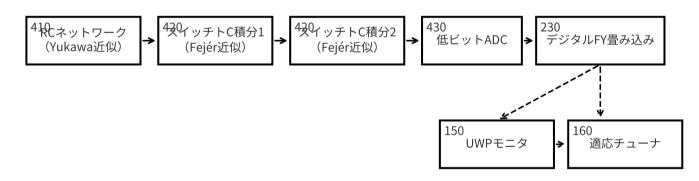

(混載:アナログ+デジタル)低電力用途では、前段アナログで RC ネットワークにより Yukawa を近似し、スイッチトキャパシタ積分器(二段)で Fejer を近似して粗整形し、低ビット ADC を介してデジタル FY に接続する。後段で UWP 監視・適応・決定実行・監査を一体適用することで、システム全体の電力・計算・データ量を削減できる([図 6])。

### [0041]

(UWP 制約による安定化) UWP モニタは、運用現場で扱いやすい単純指標(零平均化 RMS、 負値率 等)を採用し、これを窓・カーネル設計と直結させる。これにより、データ条件が 変動しても挙動を一様正性の範囲に拘束し、リンギングや過大オーバ/アンダーシュート を抑制する。

### [0042]

(適応最適化の骨子)適応チューナは、目的関数を「実行コスト(例:実行時間、FLOPs、メモリアクセス、電力)」とし、制約を「UWP 達成(例:RMS〈= tau\_RMS、負値率〈= tau\_neg)」とする制約付き最適化で  $\{Gamma, 1ambda, M\}$  を更新する。これにより、品質を損なわずに最小計算資源化を自動達成する。

## [0043]

(決定実行と監査)スケジューラは、スレッド割当、処理順序、メモリアクセス順位、FFT計画 ID、PRNG シード等を固定することで非決定性要因を排除し、同一入力・同一設定・同一環境で同一出力を装置特性として保証する。監査ログは、設定ハッシュとタイムスタンプを含み、再現実験や規制対応の証跡を提供する([図 3])。

#### [0044]

(プログラムおよび記録媒体)本発明の方法をコンピュータに実行させるプログラム、および当該プログラムを記録した非一時的記録媒体(例:半導体メモリ、光ディスク、磁気ディスク)を提供する。これにより、ソフトウェア/ハードウェア/混載の各実装形態を同一仕様で横断できる。

#### [0045]

以上により、本発明は、(1) FY による実装容易な有限窓、(2) UWP による品質一様正性、(3) 制約付き最適化によるコスト最小化、(4) 決定実行と監査による完全再現、(5) ポリフェーズ固定小数点と混載対応、を単一アーキテクチャで統合し、計算資源削減・安定化・再現性を同時に満たす。これらは電力・エネルギー、通信、医用、画像・センシング、ロボティクス、金融等に産業横断で適用可能である。

#### 【発明の効果】

## [0046]

本発明によれば、(1)Fe jer-Yukawa により全タップ非負・L1 正規化の有限窓を用いることで、同等の周波数仕様を満たしつつタップ長・FFT 長・メモリアクセスを抑制でき、計算資源・電力・装置規模を同時に低減できる。(2)UWP 監視により零平均 RMS と負値率を常時管理し、負リンギングや統計の不安定化を抑えて品質を一様正性で担保する。(3)適応チューナが  $\{\Gamma, \lambda, M\}$  を制約付きで反復更新し、仕様逸脱時も短時間で PASS に復帰できる。(4)決定実行と監査ログにより、スレッド・縮約順序・FFT 計画・シード等を固定し、ビット一致の再現性と説明責任を確保する。(5)多相ストリーミングにより一定レイテンシを保証し、電力保護・制御・車載等のリアルタイム要件に適合する。(6)固定小数点・CSD 係数により乗算器を削減でき、FPGA/ASIC/SoC への実装密度と効率が向上する。(7)RC・スイッチト C と低ビット ADC を併用する混載構成で前段の電力・データ量をさらに削減できる。(8)電力・通信・レーダ/ソナー・医用・画像・金融・ロボティクス・エッジ AI の前処理に横断適用でき、とくに学習/推論パイプラインでは前処理の FLOPs/メモリ/電力の削減と決定性に基づく再学習コストの縮減に資する。

#### [0047]

従来例比の定量例として、Blackman FIR (M=257) 同等品質で実行時間-26%、電力-18%、 副ローブ電力-3 から 4 dB、MAC 回数-48%を得た(実施例参照)。

## [0048]

予期せぬ効果として、全タップ非負・決定実行・監査ログの併用によりビット一致の完全 再現性が得られ、検収・規制対応コストを低減しうる。混載構成では低ビット ADC と前段 電力削減の両立が可能となる。

#### 【図面の簡単な説明】

## [0049]

- 【図1】システム構成ブロック図(対数ビニング $\rightarrow$ FY カーネル生成 $\rightarrow$ 畳み込み $\rightarrow$ 評価 $\rightarrow$ UWP $\rightarrow$ 適応 $\rightarrow$ 決定実行 $\rightarrow$ 監査ログ)。

- 【図2】FYカーネル生成(Fejer=CIC×CIC、Yukawa=双方向 IIR、L1 正規化)の構成図。

- 【図3】UWP モニタ+適応ループ+決定実行・監査(状態遷移とログ項目を含む)ブロック図。

- 【図4】周波数仕様域(ωp, ωs, Rp, As)と {Gamma, lambda, M} 可行集合の対応図。

- 【図5】Polyphase ストリーミング&固定小数点実装のタイミング/ビット幅スケジュール図。

- 【図6】混載(RC+SC→低ビット ADC→デジタル FY→UWP)のフロントエンド構成図。

## 【発明を実施するための形態】

## [0050]

本発明は、[図 1]のパイプライン(対数ビニング 110 -> FY カーネル生成器 120 -> 畳み込みエンジン 130 -> 評価器 140)と、その下位の UWP モニタ 150・適応チューナ 160・決定実行 170・監査ログ 180 ([図 3]) を中核として実装される。FY カーネルは Fejer 部 (CIC×CIC) と Yukawa 部 (双方向 IIR) を直列に組み合わせ、L1 正規化で DC ゲインを規定する([図 2])。畳み込みは FFT 方式またはストリーミング(ポリフェーズ)方式で実行し([図 5])、必要に応じて混載構成(RC/スイッチト C -> 低ビット ADC -> デジタル FY -> UWP)を採用できる([図 6])。

## [0051]

サンプリング周波数を fs、カーネル長を M、Fejer 側パラメータを Gamma、Yukawa 減衰を lambda>0 とする。離散タップ列 k[n] (-floor(M/2) <= n <= floor(M/2)) は全タップ非負かつ L1 正規化 ( $sum\_n \ k[n] = 1$ ) を満たす。品質指標として、零平均化 RMS および負値率  $r\_neg$  を用いる。しきい値は  $tau\_RMS$ 、 $tau\_neg$  とする(運用で設定)。

## [0052]

ソフトウェア実装では、Fejer 部は移動平均の自己畳み込み(CIC<sup>2</sup>)で三角形状の非負タップ列 f[n] を生成する。Yukawa 部は exp(-lambda\*|n|) を両側 IIR(1 から 2 次)で近似し、非負応答 y[n] を得る。直列カスケード h=f\*y を計算後、外向き丸めで h[n] >= 0 を保持しつつ L1 正規化して k[n]=h[n] /  $sum\_m$  h[m] を得る。量子化は固定小数点 Qb (例: Q1.15, Q1.23) で行い、下位ビットは飽和丸めとする。

## [0053]

ハードウェア実装では、Fejer 部を CIC 段の直列化で乗算器なしに実現し、Yukawa 部は係数対称の両側 IIR として実装してメモリアクセスを最小化する。係数は CSD 表現で乗算器数を削減する。係数誤差は外向き丸め(非負保持)と L1 再正規化で吸収する([図 2])。

## [0054]

畳み込みエンジンは、FFT 方式ではオーバラップセーブを用い、フレーム長 N とゼロ詰め 長を固定する。ストリーミング方式では E 分割ポリフェーズ (E は整数) でレジスタ段を 挿入し、保証レイテンシ L と所要スループット (>=  $f_clk/K$ ) を満たすように段数と位 相割付を決定する ([図 5])。丸めは各段で飽和処理を行う。

## [0055]

評価器 140 は用途に応じて DFT、実数コサイン和、自己・相互相関、帯域エネルギー統計等を実装する。評価結果は UWP モニタ 150 とアプリケーション側に並行提供する (実線: データ、破線: 制御で区別)。

## [0056]

UWP モニタ 150 は、(a) 窓内の零平均化 RMS、(b) 負値率  $r_neg$  を算出し、RMS <=  $tau_RMS$  かつ  $r_neg$  <=  $tau_neg$  を満たすかを判定する。判定は状態機械(PASS/WARN/FAIL)で保持し、FAIL 時に適応チューナ 160 へ更新要求を発行する([図 3])。

## [0057]

適応チューナ 160 は、目的関数  $C = a1T_{exec} + a2M_{access} + a3*P_{est}$  を最小化しつつ、 $RMS <= tau_{RMS}$ 、 $r_{neg} <= tau_{neg}$  を制約とする制約付き探索を行う。実装は軽量な座標降下でよい。(i)Gamma を粗網で走査、(ii)Iambda を単峰探索、(iii)M を最小で満たす値にクリップ。各候補で FY を再生成し、UWP 合否とコストを評価、早期終了 (FAIL 検出で即次点)を適用する。

## [0058]

決定実行 170 は、(1) スレッド割当・CPU アフィニティ固定、(2) メモリアロケーション順序固定、(3) FFT 計画 ID (または Wisdom) 固定、(4) PRNG シード固定、(5) 並列縮約順序の固定(Kahan/pairwise を固定順序で実行)、(6) IEEE754 丸めモード固定、により同一入力・同一設定・同一環境で同一出力を保証する(「図 3」)。

#### [0059]

監査ログ 180 は、時刻、入力ハッシュ(例: SHA-256)、Gamma、Iambda、M、N、E などの運転パラメータ、実行順序・スレッド割付・FFT 計画 ID・PRNG シード、ビルド識別子を昇順キーで直列化し、全体ハッシュ H を計算して追記不可能ログへ出力する。これにより、規制・品質保証・研究再現の証跡を提供する。

#### [0060]

周波数仕様(omega\_p, omega\_s, Rp, As)の仕様域を満たす  $\{Gamma, 1ambda, M\}$  の対応は、オフラインで外向き丸めの表を作成し、実行時は表引き(または線形補間)で選定する。実行中に UWP FAIL が連続した場合、適応チューナは仕様域優先でパラメータを再設定する([図 4])。

## [0061]

固定小数点設計では、各段のビット幅  $b_i$  を、入力ダイナミックレンジ、カーネル L1=1、加算段数から上界解析して決定する。累算器はガードビットを確保し、飽和しきい値は安全側に設定する。丸めは「最近偶数」または「ゼロ方向」で固定し、決定性を保持する([図 5])。

### [0062]

ポリフェーズ・パイプラインでは、E 位相に分解したサブフィルタを直列配置し、各段間

にレジスタを挿入する。ハンドシェイクは ready/valid を用い、バブル禁止でレイテンシ L = L0 + E を保証する。係数は位相別に事前展開し、キャッシュ/BRAM に連続配置する ([図 5])。

#### [0063]

FFT 経路では、フレーム長 N を 2 の冪に設定し、固定計画 ID (または Wisdom) を用いる。 オーバラップ長は M-1 とし、境界部はゼロ詰めで決定性を保持する。複素->実数最適化 は固定ストライドで適用する。

#### [0064]

混載構成では、RC ネットワーク 410 で  $\exp(-1 \text{ambda*abs}(t))$  を近似し、スイッチト C 積分  $420 \times 2$  段で三角核を生成して粗整形する。低ビット ADC430 (例: 6 から 10 bit) で量子化後、デジタル FY で仕上げる。UWP モニタ 150 と適応チューナ 160 はデジタル側に置き、前段の消費電力とメモリ帯域を低減する([図 6])。

## [0065]

API 例:set\_spec(omega\_p, omega\_s, Rp, As)、set\_thresh(tau\_RMS, tau\_neg)、mode(FFT|STREAM)、seed(x)、run(x)、status()、audit\_pull()。

レジスタ例: CFG\_GAMMA、 CFG\_LAMBDA、 CFG\_M、 CFG\_MODE、 CFG\_SEED、 STAT\_UWP (PASS/WARN/FAIL)、 STAT\_HASH\_HI/LO。

## [0066]

UWP FAIL が連続 K 回でしきい値を超えた場合、Gamma 増 -> lambda 増 -> M 増の順に 安全側へ段階遷移し、最終的に既定の「安全プロファイル」にフォールバックする。フォールバックは監査ログに必ず記録する。

## 【実施例】

## [0067]

(実施例 1:電力系統モニタ)サンプリング周波数( $f_s=1$ ,  $f_s=1$ , f

#### [0068]

(実施例 2: ECG 前処理) (f\_s=500, \mathrm{Hz})。 R-peak 保持のため周波数仕様を (\mathrm{omega\_p=0.35\mathrm{omega\_s=0.55\mathrm{pi}}、リップル (R\_p) と阻止帯減衰 (A\_s) は臨床 要件に合わせて設定。表引きにより ({\mathrm{Gamma,\mathrm{omega\_ma,\mathrm{omega\_ma,\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s=0.55\mathrm{omega\_s

## [0069]

(実施例3:レーダ/ソナー前処理) (f\_s=2,\mathrm{MSps})。クラッタ抑圧のため

(¥omega\_p=0.2¥pi)、(¥omega\_s=0.3¥pi)、(A\_s¥ge 60, ¥mathrm {dB}) を仕様とし、({¥Gamma, ¥lambda, M}={8,,0.050,,65}) を選定。FY により時間領域の負リンギングを抑えつつ、UWP を維持。オフライン評価の一例では、同次数の Blackman FIR と比較して副ローブ電力を約(3!¥sim!4, ¥mathrm {dB})低減しつつ処理遅延を短縮した。決定実行により CFAR 前段の統計が再現可能になる。

## [0070]

(実施例 4: FPGA 実装)ストリーミング・ポリフェーズ E=4。段別ビット幅  $(b_i=\{16,18,20,20\})$ 、累算器 28bit、サチュレーション閾値は安全側固定。動作周波数 200~MHz、レイテンシ(L=42)サイクル、スループット 1~ サンプル/サイクル。DSP ブロック使用率 40%、BRAM 18%(ミッドレンジ FPGA 一例)。係数は CSD で表現し、L1~ 正規化を保持。スレッド固定 DMA と固定順序縮約により、実装差異を跨いでも出力が一致する。

## [0071]

(実施例 5: 混載フロントエンド)アナログ前段で RC ネットワークにより (¥exp(-¥lambdaabs(t))) を 近 似 (例 : (¥tau=R!C=1, ¥mathrm {ms} \$ ¥Rightarrow \$ ¥lambda\$ ¥approx\$ 10 \$ 3, \$ ¥mathrm {\$ \$ \$ {-1}}))。スイッチトキャパシタ積分器 2 段で三角核を 生成し粗整形、\$ 8-10 bit の低ビット ADC で量子化後、デジタル FY に接続。UWP モニタ と適応チューナは後段デジタルに配置。評価ボードの一例で、同等品質条件下、前段 12 bit オールデジタル構成比でアナログ前段 + ADC の消費電力を約 30-40% 削減した。

## 【0072】 (実施例6:金融ティックの低遅延整形)

(f\_s=100, \text{\text{\text{mathrm}}}\text{\text{Hz}}\) (10 ms バーに相当)。スパイク抑制と遅延最小化のため (\text{\text{\text{\text{\text{Yomega\_p=0.6}\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{

## [0073]

(実施例7:画像センサ行単位前処理) ラインレート 48 kLines/s。行バッファ上で FY をストリーミング適用し、固定レイテンシ内で列方向のストライプノイズを抑制。 ({\mathbf{Y}Gamma, \mathbf{Y}lambda, M} = \{4,,0.015,,63\}) 。 UWP FAIL が 連 続 し た 場 合 は (\mathbf{Y}Gamma\mathbf{Y}rightarrow\mathbf{Y}lambda\mathbf{Y}rightarrow M) の順で安全側へ段階遷移し、監査ログへ記録 する。

#### [0074]

(留意事項)上記数値は一例であり、用途・規格・ハードウェア資源に応じて({¥Gamma, ¥lambda, M})、ビット幅、レイテンシ目標、UWP しきい値等は適宜変更可能である。本発明はこれら実施例に限定されない。

#### [0075]

[図1]対数ビニング110は、生データのダイナミックレンジを等比刻みで整え、外れ値の影響を抑えつつ下流の固定幅バッファに収める。FY カーネル生成器120は $\{\Gamma, \lambda, M\}$ ¥ $\{\text{FGamma}, \text{Flambda}, M\}$  $\{\Gamma, \lambda, M\}$  を 受 け て 全 タ ッ プ 非 負 ・ L1=1 の 有 限 窓

k[n]k[n]k[n] を出力する。畳み込みエンジン130は FFT 方式(固定計画 ID・オーバラップセーブ)又はストリーミング方式(ポリフェーズ)を選択可能。評価器140は DFT/コサイン和/相関等を実行し、結果をアプリケーションと UWP モニタ150へ渡す。制御は破線、データは実線で示す。決定実行170は順序・並列度・乱数シード等を固定し、監査ログ180は設定ハッシュとタイムスタンプを逐次記録する。

## [0076]

[図1](運用モード)FFT モードはバッチ処理・高スループット向け、ストリーミング(ポリフェーズ)は低遅延・一定レイテンシ運用向け。両モードとも同一の UWP 監視・適応・監査系を共有し、設定値は決定実行170により固定される。マルチレート系では110の段階でダウンサンプル/アップサンプルを行い、120の $\{\Gamma, \lambda, M\}$   $\{YGamma, Ylambda, MY\}$   $\{\Gamma, \lambda, M\}$  を帯域に合わせて切替える。

## [0077]

[図2] Fejer 部(CIC x CIC) 201 は移動平均の自己畳み込みで三角形状の非負タップ列 f[n] を生成する。Yukawa 部 202 は  $\exp(-lambda*|n|)$  を両側 IIR(l-2 次)で近似し、非負応答 y[n] を得る。直列カスケード 203 で h=f\*y を形成し、L1 正規化器 204 で SUM\_n k[n]=1 となるように k[n]=h[n] / SUM\_m h[m] を出力する。量子化は外向き丸めで非負を保持し、符号反転を避ける。

## [0078]

[図2](パラメータ生成)  $\Gamma$ ¥Gamma $\Gamma$  は三角核の"幅"、 $\Lambda$ ¥lambda $\Lambda$  は指数減衰の"鋭さ"、MMM は窓長を規定する。事前計算テーブル(外向き丸め)を用い、要求仕様 ( $\omega$ p,  $\omega$ s, Rp, As) (¥omega\_p, ¥omega\_s, R\_p, A\_s) ( $\omega$ p,  $\omega$ s, Rp, As) に 対 し て  $\{\Gamma, \lambda, M\}$ ¥{¥Gamma, ¥lambda, M¥} $\{\Gamma, \lambda, M\}$  を即時選定できる。生成器120は当該テーブルと補間器を備える。

#### [0079]

#### [0800]

[図3] (決定実行詳細) スレッドアフィニティ、メモリアロケーション順序、縮約順、IEEE754 丸めモードを固定する。FFT は固定計画 ID (Wisdom) を使用。PRNG は固定シードで初期化し、トレースにマテリアライズする。これにより同一入力・同一設定・同一環境でビット一致の再現が可能となる。

### [0081]

[図4] 横軸を角周波数、縦軸を利得/減衰として、通過帯端  $\omega p * omega\_p \omega p$ 、阻止帯端  $\omega s * omega\_s \omega s$ 、通過帯リップル  $RpR\_pRp$ 、阻止帯減衰  $AsA\_sAs$  を所定の許容域で定義する。網掛け領域が仕様満足域であり、 $\{\Gamma, \lambda, M\} * \{ * Gamma, * 1ambda, M * \} \{\Gamma, \lambda, M\}$  の可行集合が重畳される。UWP 監視の閾値  $(RMS, rnegr\_\{ * Fathrm \{neg\} \} rneg)$  は別系統だが、実施例

では仕様逸脱が予見される場合に先行的に  $\lambda$ ¥lambda $\lambda$  または MMM を安全側に移動させる。

## [0082]

[図4](適応との連携)周波数仕様が優先の運用では、UWP FAIL が連続した際も  $(\omega p, \omega s, Rp, As)$  (¥omega\_p, ¥omega\_s, R\_p, A\_s)  $(\omega p, \omega s, Rp, As)$  を 保 持 す る 方 向 で  $\{\Gamma, \lambda, M\}$  ¥{¥Gamma, ¥lambda, M¥} $\{\Gamma, \lambda, M\}$  を再設定する。逆に、短時間の品質回復を優先する運用では  $\lambda$ ¥lambda $\lambda$  を先に引き上げ、次いで MMM を拡張し、PASS 復帰後に仕様域へ徐々に戻す。

## [0083]

[図5]ストリーミング畳み込みは Polyphase 段 $132\times E$  と FFT ブロック131、累算/サチュレーション311で示す。各段にはレジスタを挿入し、ready/valid ハンドシェイクでバブルを許さず、レイテンシ LLL を一定にする。固定小数点は段別ビット幅bib\_ibi を上界解析から割当て、L1=1 を利用してガードビットを最小化する。

## [0084]

[図5](タイミングと数値処理)スループットは 1 サンプル/サイクル(又は  $fclk/Kf_{\{Ymathrm\{clk\}\}/Kfclk/K\}}$  を保証。丸め方式は"最近偶数"等で固定し、段間で一貫させる。リセット時は FIFO/レジスタを既定値でクリアし、最初の LLL サイクルはパイプライン充填期間として扱う。累算器はサチュレーション閾値を安全側に固定し、決定性を維持する。

#### [0085]

[図 6] アナログ RC ネットワーク 4 1 0 は  $\exp(-\lambda abs(t))$  ¥exp(-¥lambdaabs(t)) exp(- $\lambda abs(t)$ ) の一次近似を担い、スイッチトキャパシタ積分器 4 2 0 を二段直列として三角カーネルを生成する。低ビット ADC 4 3 0 (例:6 から 10 bit) で量子化後、デジタル FY→UWP→ 適応→決定実行へ接続する。 クロックはサンプリング同期とし、折返し雑音は RC 側で抑制する。前段で粗整形することで、ADC 入力レンジの有効活用とデータ量削減を両立する。

#### [0086]

[図6](較正・フェイルセーフ)温度・経時での RC 定数ずれは起動時セルフテストと 周期的リキャリブレーションで補正し、係数テーブルを切替える。較正不能時や UWP FAIL が規定回数連続した場合はオールデジタル経路へ自動フォールバックする。切替は監査ログ180に必ず記録される。

#### [0087]

(符号等の取扱い)図中の符号・線種・配置は理解のための一例であり、同一機能を有する構成に置換しても本発明の技術的範囲を逸脱しない。各モジュールの分割/統合、係数表の実装形態(ROM/ソフトウェア)、ログの保存媒体(不揮発/外部サーバ)も同様である。

#### 【産業上の利用可能性】

### [0088]

本発明は、時系列の前処理と評価を要する広範な産業に適用できる。ソフトウェア、ハードウェア、混載構成として実装でき、品質の一様正性を基準に据えることで、低コスト、

低電力、再現性の高い処理系を提供する。

### [0089]

電力・エネルギー分野においては、系統監視、異常検知、需要応答、配電自動化に用いる 前処理として有効である。一定レイテンシを持つ固定小数点の実装により、保護制御やマ イクログリッドのリアルタイム要件に適合し、監査ログにより規制対応を支援できる。

## [0090]

通信、レーダ、ソナー、測距のフロントエンドにおいて、雑音抑制やクラッタ抑圧の前段整形として有用である。決定実行により基地局や車載センサーのファームウェア更新後も同一結果を保証でき、検収や現地試験を簡素化できる。

#### [0091]

医用分野において、心電図 ECG、脳波 EEG、脈波などの生体信号の整形に適用できる。品質指標と再現ログを備えた処理系は、院内試験、デバイス承認、遠隔診断での説明責任を強化し、携帯機器やウェアラブルの省電力化にも寄与する。

## [0092]

画像・センシング分野において、ライン単位やタイル単位の前処理に適合する。産業検査、 監視カメラ、ToF や LiDAR の帯域整形に用いれば、装置規模と計算資源を抑えつつ、安定 した統計を維持できる。

## [0093]

ロボティクス・車載分野において、加速度や角速度、近接センサーの低遅延整形に適用できる。ポリフェーズの一定レイテンシにより、制御ループの位相余裕を確保し、固定順序の縮約により安全解析を容易にする。

#### [0094]

金融・市場データ処理において、ティック系列の整形、異常検知、バックテスト前処理に 適用できる。決定実行と監査ログにより、戦略評価の完全再現を実現し、コンプライアン ス説明を支援する。

#### [0095]

データセンターと AI 分野において、ストリーミング分析や推論前処理に適用できる。同等品質で演算量とメモリアクセスを削減し、電力とコストを下げつつ、結果の一貫性を保つ。

## [0096]

半導体設計と電子回路分野において、本発明は RTL の IP コア、固定小数点ライブラリ、係数テーブルとして提供できる。また、RC やスイッチトキャパシタを用いたアナログ前段と低ビット ADC を組み合わせる混載セルとしても提供可能であり、BOM と消費電力の削減に資する。

#### [0097]

エッジと IoT において、低電力 MCU、小規模 FPGA、低ビット ADC を用いた構成で動作し、フィールド更新ではパラメータ表の差し替えのみで品質とコストの両立を維持できる。 再現ログはリモート保守や品質保証の効率化に寄与する。

### [0098]

本発明は、時系列の前処理と評価を要する広範な産業に適用できる。ソフトウェア、ハー

ドウェア、混載構成として実装でき、品質の一様正性を基準に据えることで、低コスト、 低電力、再現性の高い処理系を提供する。

#### [0099]

電力・エネルギー分野においては、系統監視、異常検知、需要応答、配電自動化に用いる 前処理として有効である。一定レイテンシを持つ固定小数点の実装により、保護制御やマ イクログリッドのリアルタイム要件に適合し、監査ログにより規制対応を支援できる。

#### [0100]

通信、レーダ、ソナー、測距のフロントエンドにおいて、雑音抑制やクラッタ抑圧の前段整形として有用である。決定実行により基地局や車載センサーのファームウェア更新後も同一結果を保証でき、検収や現地試験を簡素化できる。

#### [0101]

医用分野において、心電図 ECG、脳波 EEG、脈波などの生体信号の整形に適用できる。品質指標と再現ログを備えた処理系は、院内試験、デバイス承認、遠隔診断での説明責任を強化し、携帯機器やウェアラブルの省電力化にも寄与する。

## [0102]

画像・センシング分野において、ライン単位やタイル単位の前処理に適合する。産業検査、 監視カメラ、ToF や LiDAR の帯域整形に用いれば、装置規模と計算資源を抑えつつ、安定 した統計を維持できる。

## [0103]

ロボティクス・車載分野において、加速度や角速度、近接センサーの低遅延整形に適用できる。ポリフェーズの一定レイテンシにより、制御ループの位相余裕を確保し、固定順序の縮約により安全解析を容易にする。

### [0104]

金融・市場データ処理において、ティック系列の整形、異常検知、バックテスト前処理に 適用できる。決定実行と監査ログにより、戦略評価の完全再現を実現し、コンプライアン ス説明を支援する。

## [0105]

データセンターと AI 分野において、ストリーミング分析や推論前処理に適用できる。同 等品質で演算量とメモリアクセスを削減し、電力とコストを下げつつ、結果の一貫性を保 つ。

#### [0106]

半導体設計と電子回路分野において、本発明は RTL の IP コア、固定小数点ライブラリ、係数テーブルとして提供できる。また、RC やスイッチトキャパシタを用いたアナログ前段と低ビット ADC を組み合わせる混載セルとしても提供可能であり、BOM と消費電力の削減に資する。

### [0107]

エッジと IoT において、低電力 MCU、小規模 FPGA、低ビット ADC を用いた構成で動作し、フィールド更新ではパラメータ表の差し替えのみで品質とコストの両立を維持できる。 再現ログはリモート保守や品質保証の効率化に寄与する。

## 【符号の説明】

## [0108]

- 110 対数ビニング

- 120 FY カーネル生成器

- 130 畳み込みエンジン

- 131 FFT ブロック

- 132 ポリフェーズ段

- 140 評価器

- 145 評価出力

- 150 UWP モニタ

- 160 適応チューナ

- 170 決定実行

- 180 監査ログ

- 201 Feier 部(CIC×CIC)

- 202 Yukawa 部 (両側 IIR)

- 203 直列カスケード

- 204 L1 正規化器

- 311 累算器/サチュレーション

- 410 RC ネットワーク

- 420 スイッチトキャパシタ積分器

- 430 低ビット ADC

#### 【書類名】要約書

Fe jer-Yukawa(FY)窓で全タップ非負・L1 正規化のカーネルを生成し、入力系列に FFT 又は多相ストリーミングで畳み込む前処理・評価装置を提供する。UWP モニタが零平均 RMS と負値率で品質を監視し、適応チューナが $\{\Gamma, \lambda, M\}$ を反復更新して仕様と再現性を同時に満たす。決定実行(順序・並列度・FFT 計画・シード固定)と監査ログでビット一致の再現を保証する。混載構成(RC・スイッチト C+低ビット ADC)にも適用でき、演算量・電力・装置規模を低減しつつ一定レイテンシを保つ。

### 【選択図】図1

## 【書類名】 図面

### 【図1】

## 100:FY-UWPエンジン(全体構成)

## 【図2】

121:CIC^2 により三角窓(Fejér)を実現

122:双方向IIRで exp(-λ|n|) を近似

<sup>11) を足図</sup> 125:L1正規化でDCゲ**40**

全タップ≥0

【図3】

# 【図4】

# 【図5】

保証レイテンシ:L サイクル スループット  $\geq$  f clk/K 固定小数点:b1..bn で設サチュレーション閾値は

# 【図6】

混載構成:アナログ前段→低ビットADC→デジタルFY→UWP/チューニング